Процессор

Под словом “процессор” может пониматься любое цифровое вычислительное устройство.

Большинство процессоров общего назначения имеют принципиально одинаковое устройство.

Ограничим рассмотрение микропроцессорами общего назначения, построенными на основе архитектуры x86.

x86 (англ. Intel 80x86) — архитектура процессора c одноимённым набором команд, впервые реализованная в процессорах компании Intel.

Название образовано от двух цифр, которыми заканчивались названия процессоров Intel ранних моделей — 8086, 80186, 80286 (i286), 80386 (i386), 80486 (i486). За время своего существования набор команд постоянно расширялся, сохраняя совместимость с предыдущими поколениями.

Помимо Intel архитектура также была реализована в процессорах других производителей: AMD, VIA, Transmeta, IDT и др. В настоящее время для 32-разрядной версии архитектуры существует ещё одно название — IA-32 (Intel Architecture — 32).

x86 — это CISC-архитектура. Современные процессоры включают в себя декодеры команд x86 для преобразования их в упрощённый внутренний формат с последующим их выполнением.

Реальный режим (real mode)

Классический режим адресации, использованный в первых моделях семейства. Использует сегментированную модель памяти, организованную следующим образом: адресное пространство в 1 MiB разбивается на 16-байтовые блоки, называемые параграфами. Всего параграфов в 1 MiB — 65536, что позволяет пронумеровать их 16-разрядными числами. Сегменты памяти имеют размер 65536 байт, и всегда начинаются на границе параграфа. Адрес ячейки памяти состоит из двух частей: номера параграфа, с которого начинается сегмент и смещения внутри сегмента и обычно записывается как SSSS:OOOO (Segment и Offset), где S и O — шестнадцатеричные цифры. SSSS называется сегментной компонентой адреса, а OOOO — смещением. Адрес ячейки, выдаваемый на шину, представляет собой сегментную компоненту умноженную на 16 плюс смещение. Сегментная компонента помещается в специальный регистр, называемый сегментным, а смещение в регистр IP(регистр инструкций). Микропроцессоры 8086/8088, 80186/80188 и 80286 имели четыре сегментных регистра, т.е могли работать одновременно с четырьмя сегментами памяти, имеющими определенное назначение. В 80386 добавили ещё два, не имеющих специального назначения.

Сегментные регистры и их назначение: CS — Сегмент кода. Используется для выборки команд программы; DS — Сегмент данных. Используется по умолчанию для доступа к данным; ES — Дополнительный сегмент. Является получателем данных в командах обработки строк; SS — Сегмент стека. Используется для размещения программного стека; FS — Дополнительный сегментный регистр. Специального назначения не имеет. Появился в процессоре 80386; GS — Аналогично предыдущему, но в новых процессорах с 64-битной архитектурой имеет особый статус: может использоваться для быстрого переключения контекстов. Несмотря на то, что сегментные регистры имеют специальные назначения, архитектура допускает при обращении к данным заменить один сегмент на любой другой. Сегменты кода, стека и получателя строк всегда используют регистры CS, SS и ES и не могут быть изменены.

Общий объём памяти, адресуемый в реальном режиме составляет 1048576 байт (0000:0000-F000:FFFF(00000-FFFFF)-логический адрес (физический адрес) в шестнадцатеричной системе счисления). Сегментный подход позволяет разделить всю память на 16 сегментов, начинающихся с адресов, кратных 64 Кбайт. Эти 16 сегментов называют страницами памяти. Обычно деление на страницы используется для совместного функционирования устройств, интерфейсы которых отображены на адресное пространство памяти; тогда каждое такое устройство использует одну страницу памяти, и адрес ячейки в адресном пространстве устройства будет совпадать со смещением в сегменте памяти компьютера. Так в компьютерах IBM PC страницы c 11 по 15 используются как «видеопамять»(адресное пространство видеоадаптера), а шестнадцатая страница(размещающаяся в адресах FFFF:0000 — FFFF:FFFF) получила название «области верхней памяти» (High Memory Area), которую впоследствии MS-DOS использовала для размещения своего ядра и буферов ввода-вывода, оставив больше «обычной» памяти прикладным программам. Таким образом реально доступная пользователю память составляет 640 Кбайт (первые 10 страниц).

Также в реальном режиме отсутствует защита памяти и разграничение прав доступа, поэтому он уже практически вышел из употребления. Является режимом по умолчанию для всех моделей процессоров семейства x86.

Защищённый режим (protected mode)

Более совершенный режим, впервые появившийся в процессоре 80286 и в дальнейшем многократно улучшавшийся. Имеет большое количество подрежимов, по которым можно проследить эволюцию семейства ЦП. В этом режиме поддерживается защита памяти, контексты задач и средства для организации виртуальной памяти. Аналогично реальному режиму, тут также используется сегментированная модель памяти, однако уже организованная по другому принципу: деление на параграфы отсутствует, а расположение сегментов описывается специальными структурами (таблицами дескрипторов), расположенными в оперативной памяти. Помимо базового адреса сегмента дескрипторы содержат размер сегмента (точнее, максимально доступное смещение) и различные атрибуты сегментов, использующиеся для защиты памяти и определения прав доступа к сегменту для различных программных модулей. Существует два типа дескрипторных таблиц: глобальная и локальная. Глобальная таблица описывает сегменты операционной системы и разделяемых структур данных. Локальная таблица может быть определена для каждой конкретной задачи (процесса). Сегменты памяти также выбираются все теми же сегментными регистрами; однако вместо номера параграфа сегментный регистр содержит специальную структуру (селектор), содержащую индекс дескриптора в таблице. Сам же дескриптор загружается из памяти во внутренний программно недоступный регистр (кеш), привязанный к каждому сегментному регистру и автоматически загружаемый в момент его модификации.

Каждый программный модуль, выполняемый в защищённом режиме, определяется его сегментом кода, описываемым регистром CS, который и определяет его привилегии по доступу к данным и другим модулям. Существует 4 уровня привилегий (0, 1, 2 и 3), называемых кольцами защиты. Кольцо 0 наиболее привилегированное. Оно предназначено для модулей ядра операционной системы. Кольцо 3 — наименее привилегированное, и предназначено для пользовательских программ. Кольца 1 и 2 используются лишь некоторыми операционными системами. Сегменты данных также имеют атрибуты прав доступа, дающие доступ только коду, имеющему такие же или более высокие привилегии. Система колец позволяет гибко распределять доступ к коду и данным.

Процессор 80386, появившийся в 1985 году, в отличие от своих предшественников стал 32-битным. В нём появилась возможность адресовать до 4 гигабайт памяти, что позволило создавать сегменты памяти размером во все адресное пространство. Поэтому новые операционные системы использовали вырожденную модель организации памяти, когда все сегменты начинаются с нулевого адреса. Такая модель получила название плоской (flat memory model), и адрес задается одним целым 32-разрядным числом (хотя по сути он является смещением внутри вырожденного сегмента), а сами сегменты используются исключительно для организации защиты по кольцам привилегий.

Принципиальные элементы процессора

Логические элементы

Немного повторения пройденного материала.

Логические элементы (вентили) – это простейшие транзисторные схемы, реализующие логические операции. Примерами логических операций могут служить:

- Инверсия

- Конъюнкция

- Дизъюнкция

- и т.д.

Логические операции описываются таблицами истинности, например, инверсия – унарная операция, описываемая таблицей:

| x | F |

|---|---|

| 0 | 1 |

| 1 | 0 |

Конъюнкция – бинарная операция, описываемая таблицей:

| x | y | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Дизъюнкция:

| x | y | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Наиболее часто используемые логические элементы реализуют функции штрих Шеффера (И-НЕ) и стрелка Пирса (ИЛИ-НЕ)

| x | y | S | P |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

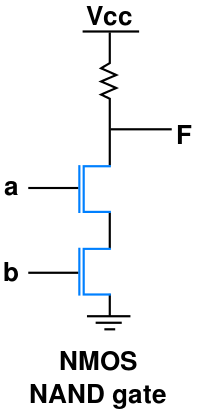

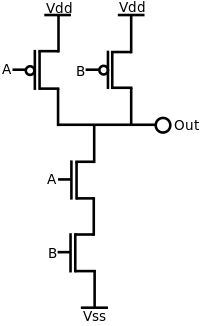

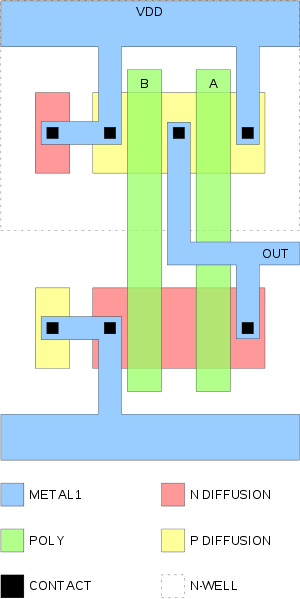

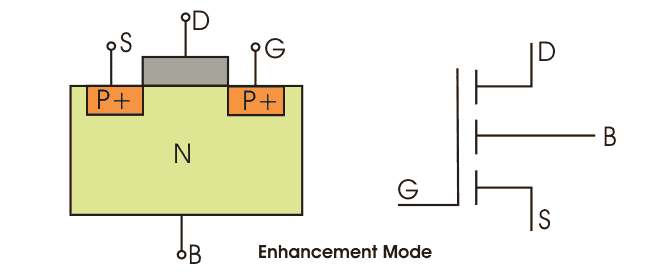

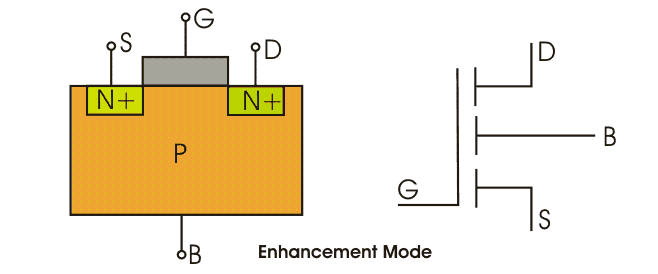

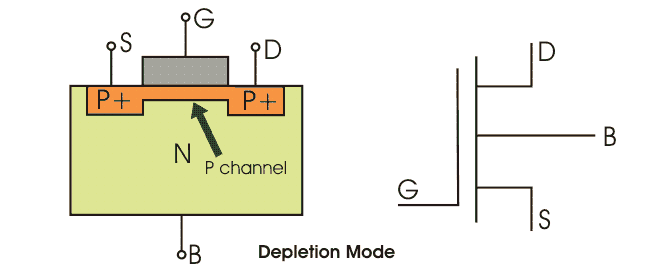

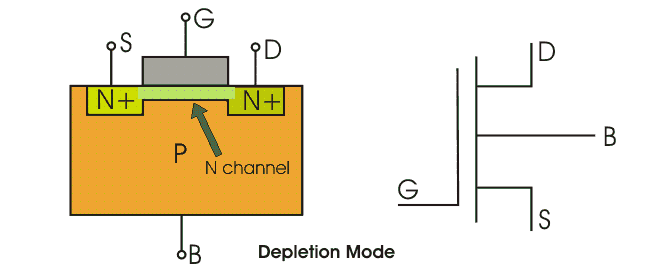

Логические элементы строятся на основе полевых транзисторов (MOSFET). Существует два типа таких транзисторов: n-тип и p-тип. N-тип проводит ток, если напряжение базы высокое, p-тип – наоборот. На основе этих двух типов строятся микросхемы типа CMOS (КМОП – комплементарная структура металл-оксид-полупроводник, она же COS-MOS), состоящие из симметрично расположенных p- и n- полевых транзисторов. Использование симметричных схем позволяет значительно уменьшить ток активации схемы и снизить энергопотребление.

Штрих Шеффера может быть реализован, например, так:

Пример логической схемы

На основе базовой логики, реализующей штрих Шеффера, можно собрать, например, полусумматор.

Таблица истинности полусумматора:

| x | y | s | p |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Соответствующие логические формулы:

\[s = x \oplus y = (\overline{x} \& y) \vee (x \& \overline{y})\] \[p = x \& y \]

Или, выражая через штриха Шеффера:

\[ s = ((x|y)|x)|((x|y)|y)\] \[ p = (x|y)|(x|y)\]

Электрическая схема:

Принципы работы полевых транзисторов

Полевые транзисторы состоят из двух полупроводниковых терминалов p- или n-типа (называемых исток (Source) и сток (Drain)), помещенных в субстрат соответственно n- или p-типа. N-тип соответствует электронной, а p-тип дырочной проводимости. Сам транзистор обозначается по типу терминалов.

Так же присутствуют два терминала, называемых база (base) и затвор (gate), которые, собственно, и обеспечивают управление транзистором.

При приложении напряжения между базой и затвором, электроны или дырки притягиваются к области затвора, создавая канал проводимости между истоком и стоком. Изменение электрического поля между базой и затвором изменяет сопротивление этого канала.

Часто терминал базы подключают напрямую к истоку.

Регистры

Простейший 1-битный регистр представляет из себя триггер. Что такое триггер? Это логическая схема, которая хранит записанное в нее значение. Простейший триггер, называемый RS-триггером, имеет следующую принципиальную схему:

Таблица истинности RS-триггера:

| R | S | Q |

|---|---|---|

| 0 | 0 | Q |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 1 | ? |

Более сложные многобитные (например 32-битные) регистры состоят из нескольких (например 32) триггеров.

Шина

Поскольку 1-битные операции не сильно интересны, входы и выходы группируются по 16, 32 и 64 (в зависимости от битности процессора). Такие группы называются шинами. Принципиально, шина – это просто набор проводов.

Вентили трех состояний

Кроме базовых логических элементов, существуют так же т.н. “буфферы”, описываемые таблицей истинности:

| x | F |

|---|---|

| 0 | 0 |

| 1 | 1 |

Они эффективно работают как усилители сигнала. В целях снижения энергопотребления и разграничения одновременного доступа к шинам, оказывается удобно иметь возможность отключать выходы буфферов. Для этого, ясно, требуется всего лишь один транзистор. Такие элементы называются tri-state, поскольку могут иметь три значения на выходе: 0, 1, и “не подключен”, обозначаемое традиционо буквой Z. tri-state элементы имеют два входа: собственно значение и вход, котролирующий их подключение. Типичный tri-state буффер описывается таблицей истинности:

| x | c | F |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | 0 |

| 1 | 0 | Z |

| 1 | 1 | 1 |

Часто такие 1-битные буфферы собираются в шины. При этом используется один контролирующий вход для всех буфферов шины.

Прерывания

Прерывание – это сигнал, сообщающий процессору о том, что некое событие требует немедленного внимания. Источником прерывания может служить аппаратное или программное обеспечение. Получив прерывание, процессор приостанавливает текущую задачу, сохраняет свое состояние (обычно регистры, недоступные для записи, такие, как PC) и передает управление в обработчик прерывания. Прерывания характеризуются цифровым кодом, и для каждого прерывания может быть отдельный обработчик. Адреса обработчиков прерываний хранятся в специально отведенном месте в оперативной памяти (обычно в кэше процессора). Программы могут регистрировать обработчики прерываний (обычно через API ОС).

- Аппаратные прерывания

- геренируются устройствами, и обычно означают, что устройство требует внимания ОС. Реализуются при помощи электрических сигналов, посылаемых на процессор с устройства. Аппаратные прерывания могут возникать в любой момент, в том числе в процессе исполнения инструкции, и требуют осторожности при обращении. Генерирование аппаратного прерывание часто называют IRQ (interrupt request, запрос прерывания). Например, нажатие клавиши на клавиатуре генерирует аппаратное прерывание.

- Программные прерывания

- генерируются либо исключением при исполнении кода, генерируемым самим процессором, либо специальной инструкцией в коде программы. Например, целочисленное деление на ноль вызывает исключение, в результате которого текущее вычисление может быть прервано.

Аппаратные прерывания изначально были придуманы чтобы отказаться от опрашивающих циклов, которые значительно менее эффективно используют процессорное время.

Сигнальные цепи устройств часто подключаются к программируемому контроллеру прерываний (PIC, APIC), который позволяет подключить несколько устройств на одну линию процессора.

Прерывания могут быть разделены на следующие категории:

- Маскируемые прерывания (IRQ) – аппаратные прерывания, которые могут быть игнорированны процессором (для игнорирования прерываний существует специальный регистр IMR – регистр маски прерываний).

- Немаскируемые прерывания (NMI) – аппаратные прерывания, которые не могут быть игнорированы. Они используются для задач с наиболее высоким прироритетом, таких как таймеры.

- Межпроцессорное прерывание (IPI) – прерывание, генерируемое одним процессором для прерывания другого процессора в мультипроцессорных системах

- Программное прерывание – прерывание, сгенерированное процессором в результате исполнения инструкции. Программные прерывания, не являющиеся исключениями, часто используются при работе в защищенном режиме для передачи управления в кольцо с бóльшими привелегиями.

- Ложное прериывание – нежелательное аппаратное прерывание, возникающее случайно в результате электрической интерференции или ошибок в аппаратном обеспечении.

Типы аппаратных прерываний

Аппаратные прерывания можно классифицировать так же по физическому методу их реализации. Можно выделить четыре основных варианта:

- Переключаемые по уровню

- Переключаемые по границе

- Гибридные

- MSI

Переключаемые по уровню прерывания инициируются поддержанием высокого либо низкого напряжения на линии прерывания. Устройство, генерирующее прерывание, повышает либо понижает напряжение на линии и поддерживает его, пока не будет обслужено. Когда оно обслужено, оно “отпускает” линию прерывания (физически отключаясь от нее), которая должна автоматически вернуться в исходное состояние.

Оригинальный стандарт слотов расширения PCI требовал использования переключаемых по уровню прерываний.

Переключаемые по границе прерывания инициируются изменением уровня напряжения на линии прерывания. Устройство, инициирующее прерывание, изменяет напряжение на линии, а затем отключается от нее (при этом линия автоматически возвращается в исходное состояние). При этом на линии возникает импульс, который и детектируется процессором или контроллером прерываний.

Стандарт слотов расширения ISA требовал переключаемых по границе прерывааний.

В обоих случаях, на одной линии прерывания может находиться несколько устройств (это называется мультиплексированием прерываний). Если процессор получает прерывание на линии, он опрашивает все устройства, подключенные к этой линии для выяснения, какое из них сгенерировало прерывание, и вызывает соответствующий обработчик.

Переключаемые по границе прерывания гораздо более чувствительны к ложным прерываниям, однако для них значительно проще реализуется мультиплексирование.

Гибридные методы – это способ избегать ложных прерываний при сохранении сравнительной плостоты мультиплексирования. Для этого, проверяется не только наличие границы, но и то, что импульс имеет определенную продолжительность.

MSI (message signaled interrupts) – это модель прерываний, не использующая выделенной линии прерывания. Вместо этого, устройство посылает цифровое сообщение на стандартную шину. Обработка такого прерывания аналогична обработке прерывания, переключаемого по границе, однако значительно более устойчиво к ложным прерываниям (поскольку цифровой сигнал в целом более устойчив к шуму) и не требует дополнительных линий для работы. Более того, одно устройство может генерировать десятки или даже тысячи (в стандарте MSI-X) различных прерываний для различных случаев.

Стандарт PCI-Express использует MSI.